Clang 编译器的主线 LLVM 15.0 中的是 Ampere Computing 对“Ampere1”的支持,这是他们的下一代服务器处理器,具有他们内部的“Ampere Cores”核心设计。

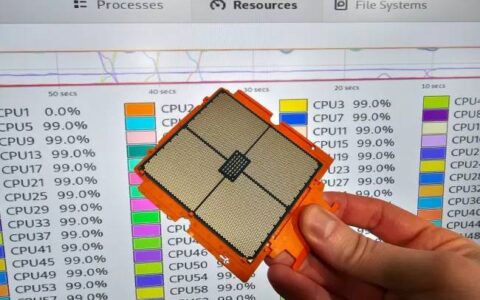

Ampere 的当前一代 Ampere Altra 和 Ampere Altra Max 处理器已经非常具有竞争力,每个插槽多达 128 个物理内核,并利用了 Arm Neoverse-N1 7nm 设计。然而,正如去年所指出的,Ampere 已经开始研究自己的核心设计,计划在 2022 年晚些时候推出。

去年的“Ampere Next-Generation”被证实是基于 5nm 的,具有符合 Arm ISA 的设计以及下一代内存 (DDR5) 和存储能力。然而,这款 Ampere Altra / Altra Max 继任者的细节仍然很清楚,它将迎来自己的核心设计。Ampere 的 2022 设计也被“Siryn”代号引用。

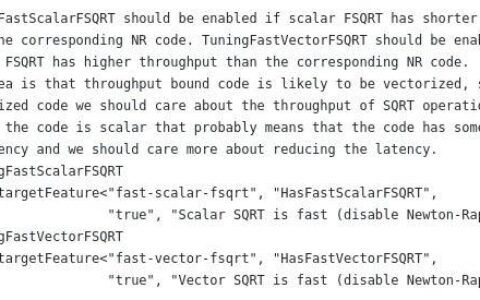

因此,今天早上我很高兴看到主线进入 LLVM 是“Ampere1”。添加了对“ampere1”目标的初始编译器支持,并且与 Armv8.6-A ISA 兼容。这至少证实了 Armv8.6-A 用于最初的内部 Ampere 内核设计而不是 Armv9,但与使用 Neoverse N1 内核的 Armv8.2 相比已经有了显着改进。

Ampere1 编译器目标确认带有 FP16 和 MTE(内存标记)扩展的 Armv8.6-A 以及启用推测屏障 (SB) 和(推测存储绕过安全 (SSBS) 选项。此 LLVM 支持修补了 Ampere-1 支持添加到GCC 编译器早在 11 月。

此补丁添加了基本的“ampere1”支持,后续补丁添加了对“native”目标选项的 Ampere1 支持。这些补丁在 Git 中,将作为今年秋季 LLVM 15.0 的一部分首次亮相.

当今年晚些时候处理器发布临近时,我们应该会听到更多关于新 Ampere CPU 内核设计的信息。目前尚不清楚“Ampere 1”是否将成为其即将推出的处理器品牌名称的一部分,或者“ampere1”是否只是暂时用作“Siryn”或占位符的替代代号——就像我们在其他地方看到的那样当涉及到对未发布 CPU 的早期编译器支持时。

原创文章,作者:校长,如若转载,请注明出处:https://www.yundongfang.com/Yun161145.html

微信扫一扫不于多少!

微信扫一扫不于多少!  支付宝扫一扫礼轻情意重

支付宝扫一扫礼轻情意重